|

╗∙ė┌FPGAĄ─ą┼╠¢▓╔╝»ŽĄĮy(t©»ng)Ą─įO(sh©©)ėŗ(j©¼)

ĮŁ╠K░▓╚½╝╝ąg(sh©┤)┬ÜśI(y©©)īW(xu©”)į║ ╝¬ÅŖ(qi©óng)ĪĪ2021/2/25 12:59:10

ĪĪĪĪ š¬ę¬Ż║ą┼╠¢▓╔╝»ŽĄĮy(t©»ng)╩Ūą┼╠¢ŽĄĮy(t©»ng)ųąųžę¬Ą─ę╗Łh(hu©ón)�����Ż¼į┌ėŗ(j©¼)╦ŃÖC(j©®)╝░ą┼╠¢╠Ä└Ēæ¬(y©®ng)ė├ÅVĘ║Ą─Į±╠ņ�����Ż¼ą┼╠¢▓╔╝»Ą─▒žę¬ąįĘŪ│Ż├„’@����ĪŻļSų°ėŗ(j©¼)╦ŃÖC(j©®)╝░ą┼╠¢ŽĄĮy(t©»ng)Ą─░l(f©Ī)š╣Ż¼─┐Ū░ą┼╠¢▓╔╝»ŽĄĮy(t©»ng)╝║▒╗ÅVĘ║æ¬(y©®ng)ė├ė┌╣żśI(y©©)��ĪóĮ╠ė²���ĪóųŪ─▄ųŲįņ║═└ū▀_(d©ó)Ą╚ČÓéĆŅI(l©½ng)ė“��ĪŻ×ķ┴╦─▄ē“ØMūŃ─ŻöMą┼╠¢öĄ(sh©┤)ō■(j©┤)īŹ(sh©¬)Ģr▓╔╝»Ą─ę¬Ū¾�����Ż¼▒Š╬─╠ß│÷┴╦ė╔¼F(xi©żn)ł÷┐╔ŠÄ│╠ķTĻć┴ąŻ©FPGAŻ®���ĪóĖ▀╦┘öĄ(sh©┤)─Ż▐D(zhu©Żn)ōQŲ„║═USBĮė┐┌ĮM│╔Ą─═©ė├ą┼╠¢▓╔╝»ŽĄĮy(t©»ng)įO(sh©©)ėŗ(j©¼)ĘĮ░ĖĪŻįO(sh©©)ėŗ(j©¼)┴╦ęįFPGA×ķ║╦ą─▓┐╝■Ą─ą┼╠¢▓╔╝»ŽĄĮy(t©»ng)��Ż¼īŹ(sh©¬)¼F(xi©żn)öĄ(sh©┤)ō■(j©┤)Ą─īŹ(sh©¬)Ģr▓╔╝»��Īó┤µā”���ĪŻ╦³Ą─ā×(y©Łu)³c(di©Żn)╩Ūö[├ō┴╦▄ø╝■“ī(q©▒)äė┐žųŲ�Ż¼ą┼╠¢Ą─▓╔╝»é„▌ö▓╔ė├╚½ė▓╝■Ą─▓┘ū„ĘĮ╩ĮŻ¼╩╣ŽĄĮy(t©»ng)Ė³╝ėĘĆ(w©¦n)Č©�����ĪóĖ▀ą¦���Ż¼USBĮė┐┌ū„×ķöĄ(sh©┤)ō■(j©┤)é„▌ö?sh©┤)─Įė┐┌��Ż¼▒ŻūC┴╦öĄ(sh©┤)ō■(j©┤)Ą─Ė▀╦┘ĘĆ(w©¦n)Č©é„▌öĪŻ

ĪĪĪĪ

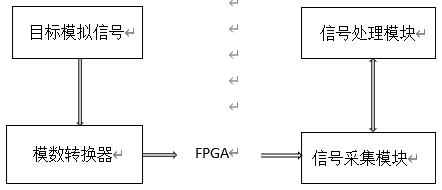

ĻP(gu©Īn)µIį~Ż║öĄ(sh©┤)ō■(j©┤)▓╔╝»�����Ż╗FPGA���Ż╗ą┼╠¢▓╔╝»

ĪĪĪĪ

ĪĪĪĪ

1ŽĄĮy(t©»ng)┐é¾wĮY(ji©”)śŗ(g©░u)

ĪĪĪĪ

▒Š╬─╠ß│÷Ą─ą┼╠¢▓╔╝»ŽĄĮy(t©»ng)ų„ę¬╩Ū└¹ė├FPGAąŠŲ¼┐žųŲ─ŻöĄ(sh©┤)▐D(zhu©Żn)ōQąŠŲ¼ī”─┐ś╦(bi©Īo)─ŻöMą┼╠¢▀M(j©¼n)ąą▓╔śė��Ż¼īó─ŻöMą┼╠¢▐D(zhu©Żn)ōQöĄ(sh©┤)ūųą┼╠¢║¾��Ż¼īæ╚ļĄĮUSBĮė┐┌ąŠŲ¼ųąīóöĄ(sh©┤)ō■(j©┤)é„▌ö?sh©┤)ĮPCųą��Ż¼└¹ė├▄ø╝■ŠÄīæ╚╦ÖC(j©®)Į╗╗źĮń├µ���Ż¼īóą┼╠¢öĄ(sh©┤)ō■(j©┤)▀M(j©¼n)ąą┤µā”����ĪŻą┼╠¢▓╔╝»─ŻēKĄ─įO(sh©©)ėŗ(j©¼)╣”─▄╩ŪīŹ(sh©¬)¼F(xi©żn)ą┼╠¢▓╔╝»┼cĘų╬÷�Ż¼═©▀^ADC▀M(j©¼n)ąą─ŻöĄ(sh©┤)▐D(zhu©Żn)ōQŻ¼īŹ(sh©¬)¼F(xi©żn)öĄ(sh©┤)ō■(j©┤)▓╔╝»║═▓╔śėöĄ(sh©┤)ō■(j©┤)Ą─┤µā”���ĪŻ

ĪĪĪĪ

ĪĪĪĪ

łD1ŽĄĮy(t©»ng)┐é¾w┐“╝▄

ĪĪĪĪ

2ą┼╠¢─ŻēKĘĮ░ĖĘų╬÷

ĪĪĪĪ

2.1ą┼╠¢▓╔╝»─ŻēKĘĮ░ĖĘų╬÷

ĪĪĪĪ

ą┼╠¢▓╔╝»─ŻēK╩Ūėŗ(j©¼)╦ŃÖC(j©®)┼c═ŌĮń▀BĮėĄ─ś“┴║�����Ż¼ę▓ĘQą┼╠¢½@╚Ī─ŻēK���ĪŻų„ę¬═Ļ│╔ī”─┐ś╦(bi©Īo)─ŻöMą┼╠¢▓╔╝»Ż¼▓óīóų«▐D(zhu©Żn)ōQ│╔öĄ(sh©┤)ūųą┼╠¢▀M(j©¼n)ąą┤µā”����ĪŻįō─ŻēKĄ─ų„ę¬╚╬äš(w©┤)╩ŪīŹ(sh©¬)¼F(xi©żn)─ŻöMą┼╠¢Ą─öĄ(sh©┤)ūų▓╔╝»Ż¼╝┤▀M(j©¼n)ąą─ŻöĄ(sh©┤)▐D(zhu©Żn)ōQ���Ż¼ęį▒Ń▀M(j©¼n)ąąą┼╠¢Ą─╠Ä└Ē����Ż¼▒ŠįO(sh©©)ėŗ(j©¼)▓╔ė├─ŻöĄ(sh©┤)▐D(zhu©Żn)ōQąŠŲ¼Ż©ADCŻ®üĒīŹ(sh©¬)¼F(xi©żn)ĪŻ─┐Ū░��Ż¼ų„┴„ą┼╠¢▓╔╝»ŽĄĮy(t©»ng)┤¾ČÓ▓╔ė├MCU╗“š▀DSPū„×ķ║╦ą─▓┐╝■üĒ▀M(j©¼n)ąąą┼╠¢▐D(zhu©Żn)ōQ���Ż¼┤µā”Ų„║═Ųõ╦¹═Ōć·ļŖ┬ĘüĒ═Ļ│╔öĄ(sh©┤)ō■(j©┤)▓╔╝»�ĪŻĄ½╩Ū�Ż¼▓╗šō╩Ūå╬Ų¼ÖC(j©®)▀Ć╩ŪDSPČ╝ėą╚▒³c(di©Żn)Ż║å╬Ų¼ÖC(j©®)ļm╚╗ųĖ┴ŅžSĖ╗Ż¼ŠÄ│╠║åå╬��Ż¼ņ`╗ŅĄ─┐žųŲĘĮ╩Į�����Ż¼Ą½▀\(y©┤n)ąą╦┘Č╚┬²��Ż¼ĘĆ(w©¦n)Č©ąį▌^▓Ņ�Ż¼┐╣Ė╔ö_─▄┴”▌^Ą═�����Ż¼śO┤¾ĄžŽ▐ųŲ┴╦ADCĄ─▓╔śė╦┘Č╚���Ż¼ī”ė┌─┐Ū░ÅŖ(qi©óng)š{(di©żo)Ė▀╦┘ą┼╠¢╠Ä└ĒĄ─Į±╠ņęčĮø(j©®ng)▓╗╠½▀mė├┴╦����ĪŻČ°DSPąŠŲ¼ļm╚╗╠Ä└Ē╦┘Č╚▌^┐ņŻ¼Ą½DSPąŠŲ¼Ą─═©ė├▌ö╚ļ▌ö│÷Įė┐┌▌^╔┘�����Ż¼╣”║─▌^┤¾���Ż¼▓óŪęī”═Ōć·įO(sh©©)éõĄ─┐žųŲ─▄┴”▌^╚§�ĪŻŽÓĘ┤��Ż¼F(xi©żn)PGAŻ©┐╔ŠÄ│╠▀ē▌ŗŲ„╝■Ż®Š▀ėąMCU║═DSP╦∙¤oĘ©▒╚öMĄ─ā×(y©Łu)ä▌��Ż¼╦³ė▓╝■▓╔ė├▓óąąÖC(j©®)ųŲ����Ż¼į┌ąį─▄║═╠Ä└Ē╦┘Č╚╔Žā×(y©Łu)ä▌├„’@Ż¼▓óŪęŠÄ│╠║åå╬�����Ż¼įO(sh©©)ėŗ(j©¼)ņ`╗Ņ����Ż¼ĢrńŖŅl┬╩Ė▀Ż¼┐╣Ė╔ö_─▄┴”ÅŖ(qi©óng)Ż¼ĘĆ(w©¦n)Č©ąį║├Ą─ā×(y©Łu)³c(di©Żn)�����ĪŻ╠žČ©Ą─▀ē▌ŗ╣”─▄ė╔ė├æ¶═©▀^ė▓╝■├Ķ╩÷šZčįŻ©HDLŻ®īŹ(sh©¬)¼F(xi©żn)�Ż¼įO(sh©©)ėŗ(j©¼)ņ`╗ŅŻ¼╣”─▄┐╔ęįĖ³Ė─��ĪŻ┤╦═Ō���Ż¼F(xi©żn)PGA▀Ćėą┤¾┴┐┐╔ŠÄ│╠▀ē▌ŗĄ─Ų¼╔ŽŽĄĮy(t©»ng)��Ż¼ų„ę¬░³└©PLLŻ©µiŽÓŁh(hu©ón)Ż®─ŻēK║═┤µā”å╬į¬����Ż¼┐╔×ķ┐éŠĆ��Īó─ŻēK«a(ch©Żn)╔·ĢrńŖ�����ĪŻę“┤╦���Ż¼ FPGAĄ─▀@ą®╠Ä└Ē╦┘Č╚┐ņ║═┤µā”╠žąį╩╣ŲõĘŪ│Ż▀m║Žė├ū„ADCĄ─┐žųŲįO(sh©©)éõŻ¼ęįīŹ(sh©¬)¼F(xi©żn)Ė▀╦┘ą┼╠¢▓╔╝»║═┤µā”┐žųŲĪŻ▒Š╬─ęįFPGA×ķ║╦ą─┐žųŲŲ„���Ż¼įO(sh©©)ėŗ(j©¼)┴╦öĄ(sh©┤)ō■(j©┤)▓╔╝»ŽĄĮy(t©»ng)����Ż¼┐žųŲADCī”öĄ(sh©┤)ō■(j©┤)▓╔śė�Ż¼▓óīó▓╔śė║¾Ą─öĄ(sh©┤)ō■(j©┤)┤µā”ĄĮSRAM┤µā”Ų„ųąŻ¼ęįīŹ(sh©¬)¼F(xi©żn)öĄ(sh©┤)ō■(j©┤)▓╔╝»║═┤µā”Ą─╣”─▄�����ĪŻ

ĪĪĪĪ

2.2öĄ(sh©┤)ō■(j©┤)╠Ä└Ē─ŻēKĘĮ░ĖĘų╬÷

ĪĪĪĪ

į┌öĄ(sh©┤)ūųą┼╠¢╠Ä└ĒĘĮ├µ�����Ż¼─┐Ū░ėą╦─ĘNīŹ(sh©¬)¼F(xi©żn)ĘĮĘ©��Ż¼ų„ę¬░³└©╩╣ė├öĄ(sh©┤)ūųą┼╠¢╠Ä└Ē▄ø╝■��ĪóąŠŲ¼�Īóå╬Ų¼ÖC(j©®)ĪóFPGAĄ╚��ĪŻ

ĪĪĪĪ

1. ╩╣ė├│Żė├Ą─öĄ(sh©┤)ūųą┼╠¢╠Ä└Ē▄ø╝■╩Ūmatlab�ĪóLabVIEWĄ╚▄ø╝■ŠÄīæöĄ(sh©┤)ūųą┼╠¢╠Ä└Ē▄ø╝■üĒīŹ(sh©¬)¼F(xi©żn)öĄ(sh©┤)ūųą┼╠¢╠Ä└Ē���ĪŻ╦³Ą─╚▒³c(di©Żn)╩Ū╠Ä└Ē╦┘Č╚╩▄ėŗ(j©¼)╦ŃÖC(j©®)CPU╠Ä└ĒĀŅæB(t©żi)Ą─ė░ĒæŻ¼ŽĄĮy(t©»ng)¾wĘe┤¾��Ż¼│╔▒ŠĖ▀����ĪŻę“Ųõ═©ė├ąį║═┐╔ęŲų▓ąį║├Ż¼öĄ(sh©┤)ō■(j©┤)Įė┐┌ŅÉą═žSĖ╗��Ż¼ų„ę¬▀mė├ė┌Į╠īW(xu©”)║═┐Ųčą��ĪŻ

ĪĪĪĪ

2. ▓╔ė├╠ž╩ŌĄ─öĄ(sh©┤)ūųą┼╠¢╠Ä└ĒąŠŲ¼Ż©DSPŻ®����ĪŻ▀@ĘNąŠŲ¼ę╗░ŃÅS╝ę═©▀^ā╚(n©©i)▓┐ė▓╝■ļŖ┬ĘįO(sh©©)ėŗ(j©¼)īŹ(sh©¬)¼F(xi©żn)╠žČ©╣”─▄Ą─öĄ(sh©┤)ūųą┼╠¢╠Ä└Ē╣”─▄Ż¼Š▀ėą└^│ąąį║├����Ż¼▀\(y©┤n)╦Ń╦┘Č╚┐ņĄ─ā×(y©Łu)³c(di©Żn)Ż¼Ą½ėųŠ▀ėą╣”─▄▌^å╬ę╗���Ż¼ārĖ±▌^Ė▀Ż¼æ¬(y©®ng)ė├▓╗ņ`╗ŅĄ─╚▒³c(di©Żn)����ĪŻ│ŻęŖŅÉą═Ą─ąŠŲ¼īŻķTė├ė┌FFT���Ż¼ŠĒĘeŻ¼Ė„ĘNöĄ(sh©┤)ūų×V▓©║═Ųõ╦¹ŽÓĻP(gu©Īn)╦ŃĘ©�����ĪŻ═©│Żė├ė┌ī”╝ė╣żėą▌^Ė▀ę¬Ū¾Ą─æ¬(y©®ng)ė├ųą����ĪŻ

ĪĪĪĪ

3. ▓╔ė├MCU▀M(j©¼n)ąąöĄ(sh©┤)ūųą┼╠¢╠Ä└ĒŻ¼å╬Ų¼ÖC(j©®)ļm╚╗ŠÄīæ│╠ą“║åå╬�����Ż¼╚▌ęūķ_░l(f©Ī)���Ż¼Ą½╩Ū��Ż¼Ųõ╠Ä└Ē╦┘Č╚▌^┬²��Ż¼ĘĆ(w©¦n)Č©ąįę▓▌^▓Ņ�����Ż¼ų╗─▄īŹ(sh©¬)¼F(xi©żn)ę╗ą®║åå╬Ą─���Īóī”Š½Č╚ę¬Ū¾▓╗Ė▀Ą─öĄ(sh©┤)ūųą┼╠¢╠Ä└Ē�����Ż¼ī”ė┌▌^Å═(f©┤)ļsą┼╠¢▓╗─▄▓╔ė├å╬Ų¼ÖC(j©®)���ĪŻ

ĪĪĪĪ

4. ▓╔ė├═©ė├Ą─FPGA╠Ä└ĒąŠŲ¼ĪŻė╔ė┌─┐Ū░FPGAį┌ąį─▄║═╠Ä└Ē╦┘Č╚╔ŽĄ─ā×(y©Łu)ä▌��Ż¼F(xi©żn)PGAį┌DSPŅI(l©½ng)ė“æ¬(y©®ng)ė├įĮüĒįĮÅVĘ║��ĪŻ▀@ĘNFPGA╠Ä└ĒąŠŲ¼Ą─╠ž³c(di©Żn)╩Ū▓╔ė├▓óąąÖC(j©®)ųŲ���Ż╗ąŠŲ¼ā╚(n©©i)▓┐ėąīŻė├Ą─ė▓╝■│╦Ę©Ų„���Ż¼┐╔ęįīŹ(sh©¬)¼F(xi©żn)┐ņ╦┘ą┼╠¢╠Ä└ĒŻ¼─▄ē“═Ļ│╔Å═(f©┤)ļsĄ─DSP╚╬äš(w©┤)�����ĪŻ

ĪĪĪĪ

┼cŪ░╚²ĘNīŹ(sh©¬)¼F(xi©żn)ĘĮ╩ĮŽÓ▒╚Ż¼ FPGAąŠŲ¼ĮY(ji©”)śŗ(g©░u)ė╔ė┌▓╔ė├▓óąąÖC(j©®)ųŲ����Ż¼į┌ąį─▄║═╠Ä└Ē╦┘Č╚╔Žā×(y©Łu)ä▌├„’@�Ż¼▓óŪęŠÄ│╠║åå╬Ż¼įO(sh©©)ėŗ(j©¼)ņ`╗Ņ���Ż¼┐╣Ė╔ö_─▄┴”ÅŖ(qi©óng)�����Ż¼ĘĆ(w©¦n)Č©ąį║├Ą─ā×(y©Łu)³c(di©Żn)�Ż¼ĘŪ│Ż▀m║ŽĖ▀╦┘öĄ(sh©┤)ūųą┼╠¢╠Ä└Ē����ĪŻį┌╣żū„Ą─Ą┌ę╗ļAČ╬Ż¼▓╔śėöĄ(sh©┤)ō■(j©┤)═©▀^FPGAĮė┐┌é„▌ö?sh©┤)ĮPCŲĮ┼_�Ż¼ęįīŹ(sh©¬)¼F(xi©żn)öĄ(sh©┤)ūųą┼╠¢╠Ä└ĒĪŻį┌Ą┌Č■ļAČ╬��Ż¼ęį═©ė├Ą─FPGAąŠŲ¼ū„×ķ║╦ą─┐žųŲŲ„üĒįO(sh©©)ėŗ(j©¼)öĄ(sh©┤)ō■(j©┤)╠Ä└Ē─ŻēK�����Ż¼▓óįO(sh©©)ėŗ(j©¼)FPGA▄ø╝■üĒ═Ļ│╔öĄ(sh©┤)ūųą┼╠¢╠Ä└Ē╣”─▄�����ĪŻ

ĪĪĪĪ

3Ė▀╦┘öĄ(sh©┤)ō■(j©┤)┤µā”Ż©╬┤═ĻŻ¼Ž┬ę╗ĒōŻ®

ĪĪĪĪ

|